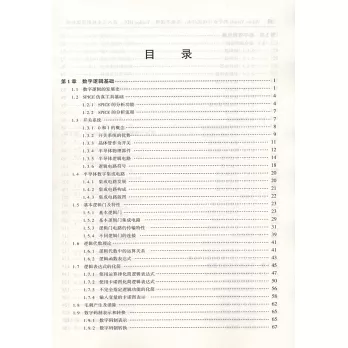

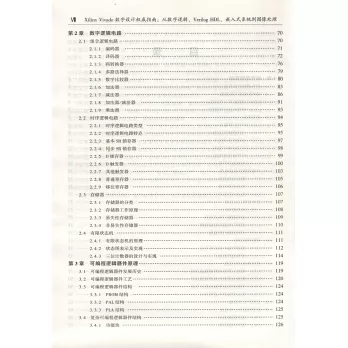

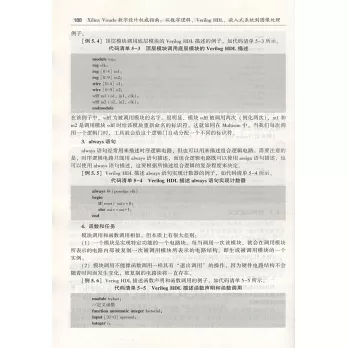

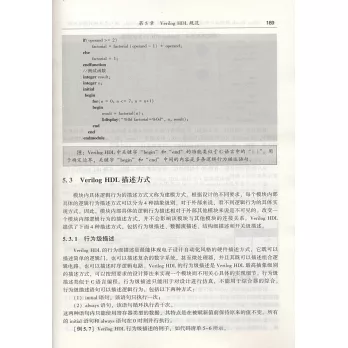

本書以Xilinx公司的Vivado 2018集成開發環境作為複雜數字系統設計的平台,以基礎的數字邏輯和數字電路知識為起點,以Xilinx 7系列可編程邏輯器件和Verilog HDL為載體,詳細介紹了數字系統中基本邏輯單元RTL描述方法。在此基礎上,實現了複雜數字系統設計、數模混合系統設計和基於Cortex-M1處理器軟核的片上嵌入式系統設計。全書共10章,內容主要包括數字邏輯基礎、數字邏輯電路、可編程邏輯器件原理、Vivado集成開發環境設計流程、Verilog HDL語言規範、基本數字邏輯單元Verilog HDL描述、複雜數字系統設計和實現、數模混合系統設計、片上嵌入式系統的構建和實現,以及圖像採集、處理系統的構建和實現。本書適合於需要系統掌握Verilog HDL和Vivado集成開發環境基本設計流程的初學者,同時也適用於需要掌握ARM嵌入式系統軟體和硬體設計方法的嵌入式開發工程師。

天天爆殺

天天爆殺  今日66折

今日66折

博客來

博客來 博客來

博客來 博客來

博客來 博客來

博客來 博客來

博客來